今回は、Lattice DiamondでVHDL記述をした後に、ModelSimというソフトウェアを使って動作シミュレーションを行う方法について解説します。

ちなみに、筆者はFPGA初心者で、備忘録として開発環境を整える方法をブログとして残しているので、多少間違っている点などもあるかもしれませんのでご了承ください。

動作シミュレーションを行うまでの手順は主に以下のようになっています。

①プログラム、テストベンチを作成する ← 別記事解説

②ModelSimでプロジェクトを作成

③コンパイルを行い、シミュレーションを行う

本記事は、Lattice Diamondバージョン:3.12での動作確認結果になります。

VHDLプログラム、テストベンチを作成する

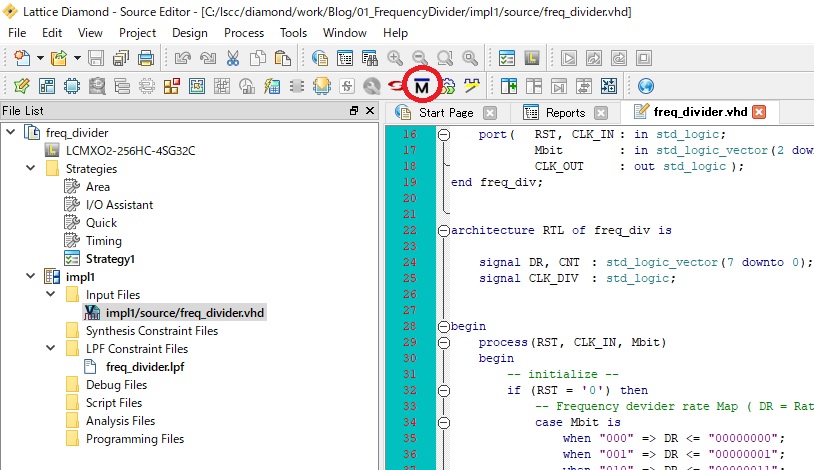

VHDLプログラムを作成

まずは、実現したい動作をVHDLプログラムで記述していきます。

今回は、以下の記事で作成した”frec_divider.vhd”というファイルを作成したとします。

VHDLファイル作成までの手順がわからない場合は、以下の記事をご確認ください。

テストベンチを作成

次に、テストベンチを作成していきます。テストベンチとは、動作確認用のプログラムのことで、今回の例では外部からクロック信号を入れてあげて、出力信号が意図した出力が出るか確認します。

今回は、以下の記事で作成した”tb_freq_divider.vhd”というファイルを作成したとします。

ここで一点注意事項として、テストベンチのVHDLファイルについては、プロジェクトに入れないように注意してください。コンパイル等で引っ掛かり、シミュレーションができなくなります。

ModelSimでプロジェクトを作成

動作シミュレーションを行うために、まずはModelSimを起動し、プロジェクトを作成していきます。

①ModelSimを起動

ModelSimを起動します。Lattice Diamond上の以下のような”M”の字のアイコンをクリックします。”Tools”→”ModelSim Lattice-Edition”からも起動可能です。

Lattice Diamond経由でなくても、直接”Mentor ModelSim Lattice Edition”を起動しても使用できます。この場合は、作業ディレクトリの指定を最初に行う必要があります。

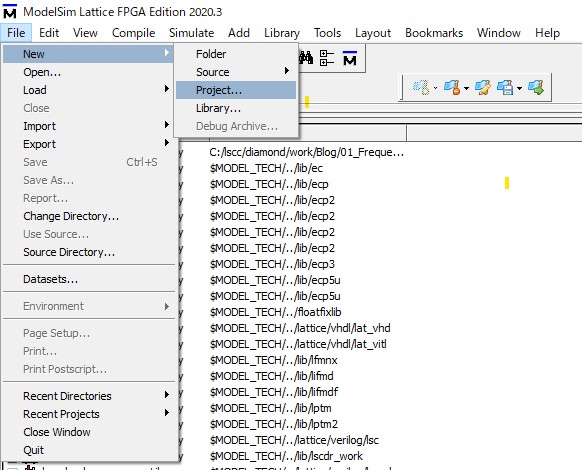

②プロジェクトファイルを作成する

「File」→「New」→「Project」と押していきプロジェクトファイルを作成します。

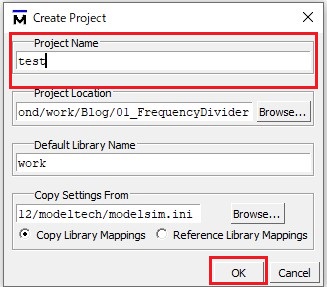

③プロジェクト名を入力

「Create Project」というウィンドウが開くので、プロジェクト名を入力して”OK”を押します。

今回は適当に”test”と入れています。

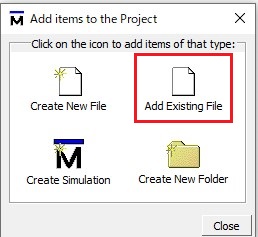

③プロジェクトに追加するファイルを選択

“Add items to Project”というウィンドウが開くので、ファイルを追加していきます。この画面の右上の”Add Existing File”をクリックします。

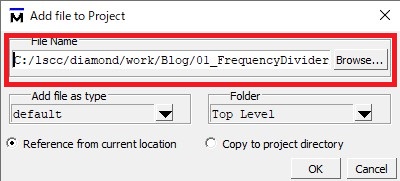

“Add file to Project”というウィンドウが開くのでファイルを追加していきます。”Browse”ボタンを押して、作成したVHDLファイルとテストベンチファイルを追加していきます。

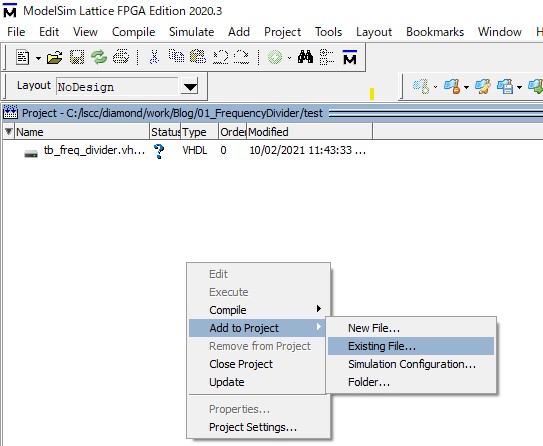

後からファイルを追加したくなった場合は、projectウィンドウ上で右クリックをして以下の写真のように”Add to Project”→”Existing File”と選んで行きます。その後は同じ手順です。

コンパイルをする

シミュレーションを行う前にインポートしたファイルのシミュレーションを行います。

①コンパイルを行う

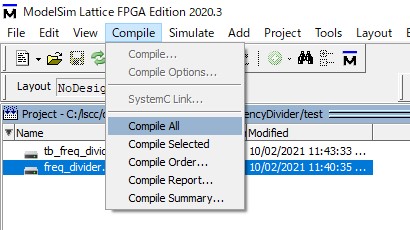

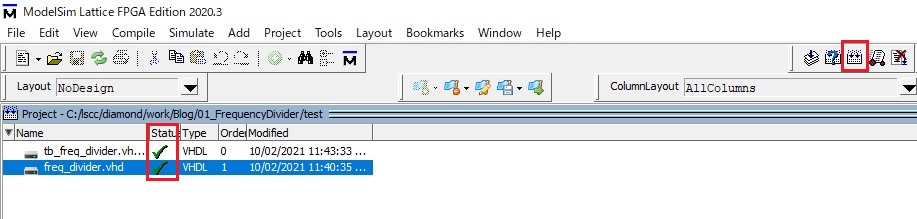

「Compile」→「Compile All」を押してコンパイルを行います。または、「Compile All」のアイコンを押します。コンパイルがうまくいくと、ファイル名の脇のステータスにチェックマークが入ります。

②シミュレーションのセットアップ

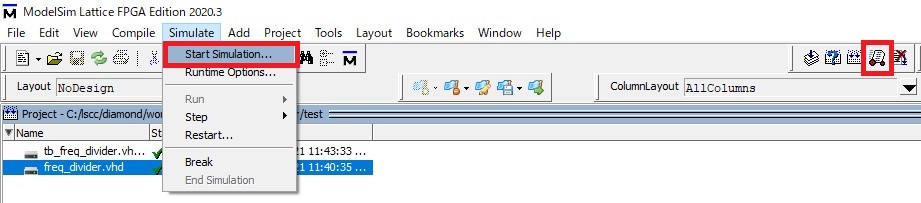

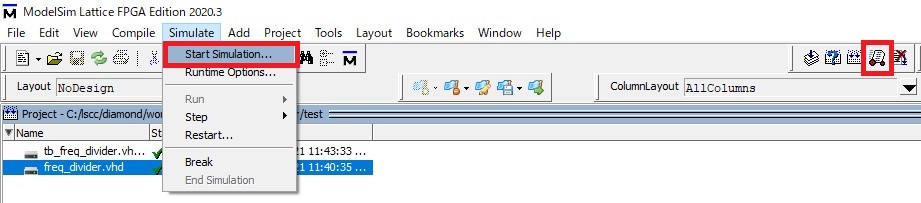

“Simulation”→”Start Simulation”と押していきます。または、”Start Simulation”のアイコンをクリックします。

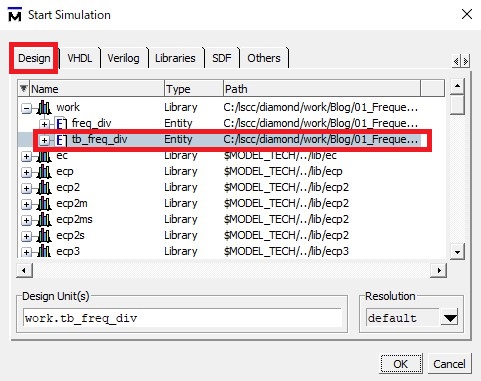

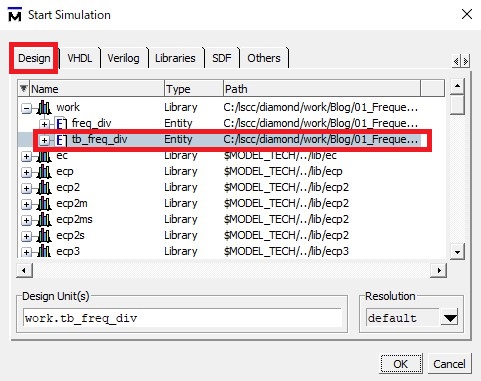

“Start Simulation”ウィンドウが開きます。”Design”タブの中の”work”というフォルダを展開し、テストベンチプログラム(今回は”tb_freq_div”)を選択します。

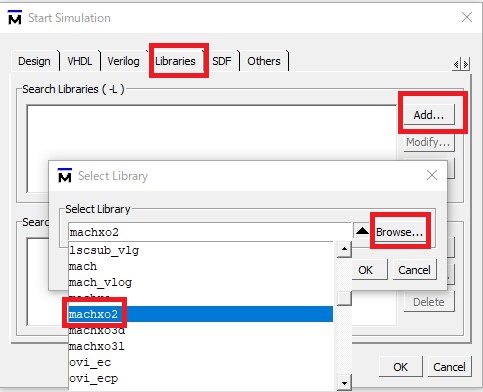

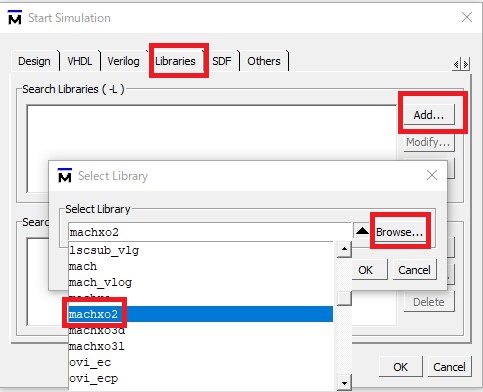

“Libraries”タブに移動し、ライブラリを選んで行きます。”Add”→”Brows”と押していき、今回使用するデバイスを選んで行きます。今回はmachxo2を選んでます。また、verilogの場合は、”ovi_machxo2″問う感じでovi_が付いたものを選びます。

シミュレーションをする

①シミュレーションのセットアップ

“Simulation”→”Start Simulation”と押していきます。または、”Start Simulation”のアイコンをクリックします。

“Start Simulation”ウィンドウが開きます。”Design”タブの中の”work”というフォルダを展開し、テストベンチプログラム(今回は”tb_freq_div”)を選択します。

“Libraries”タブに移動し、ライブラリを選んで行きます。”Add”→”Brows”と押していき、今回使用するデバイスを選んで行きます。今回はmachxo2を選んでます。また、verilogの場合は、”ovi_machxo2″問う感じでovi_が付いたものを選びます。

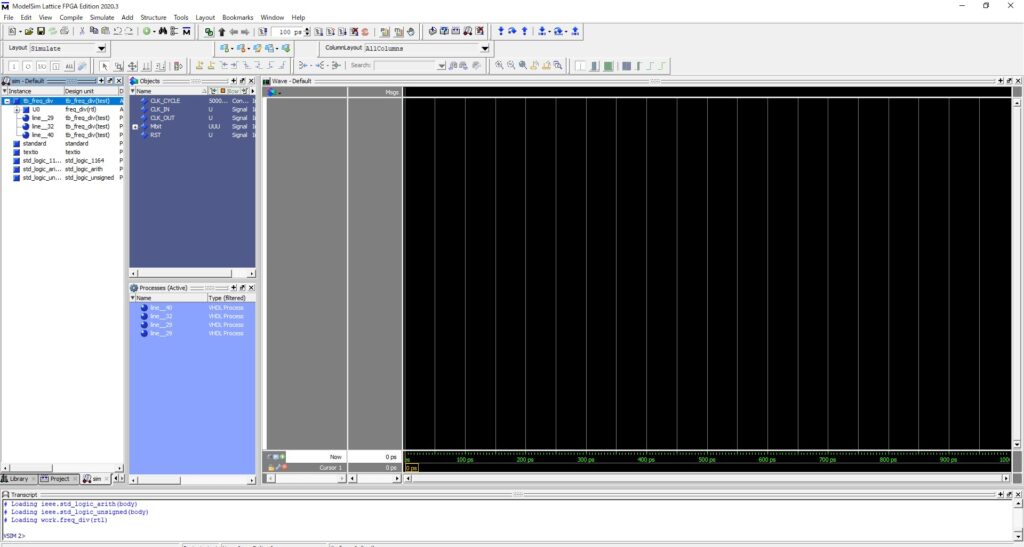

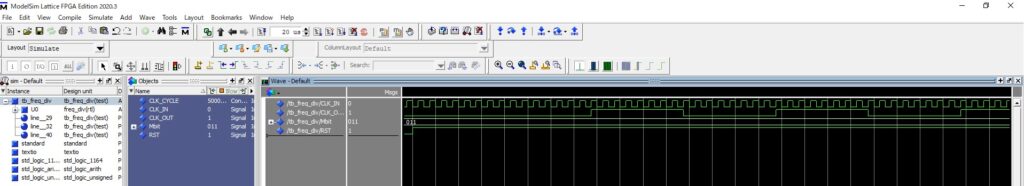

以下のようなシミュレーション画面が開きます。

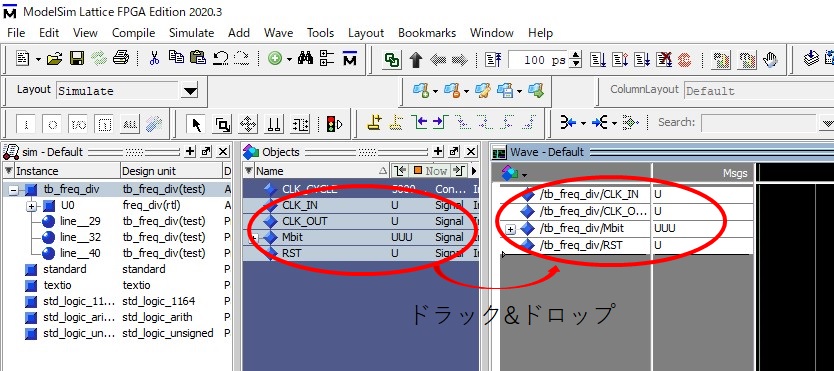

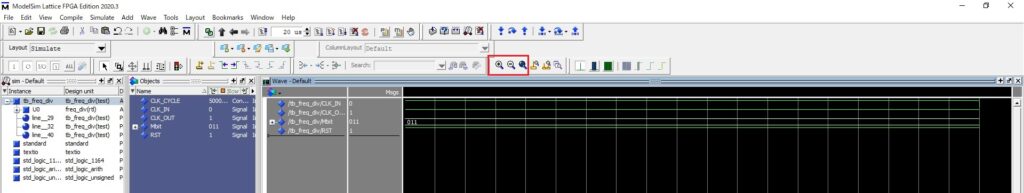

②観測したい信号をドラック&ドロップ

観測したい信号名を”object”ウィンドウから”wave”ウィンドウにドラック&ドロップします。

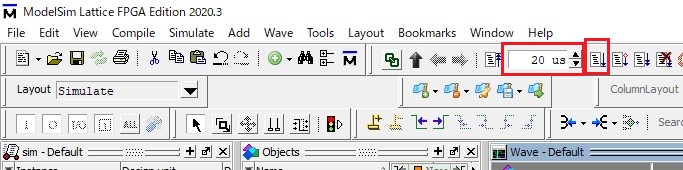

③シミュレーション時間を入力してシミュレーションスタート

シミュレーション時間を入力します。例では20 usとしています。ここで注意点としては、数字と単位の間にスペースを入れることです。

すぐわきの”Run”ボタンを押してスタートします。

④スケールを調整し波形を確認

シミュレーション直後は全体が表示されていないので、虫眼鏡マークで全体を表示したり、見たい部分を拡大したりします。

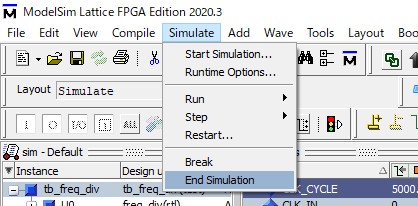

プログラムを修正して再シミュレーション

プログラムを修正して再シミュレーションする時は、”Simulation”→”End Simulation”と押して、一旦シミュレーションを終了する必要があります。その後は最初の手順から同じことをやるだけです。(何回も修正を重ねるときはちょっとめんどくさいです)

シミュレーションを無事に行うことができました。これで、作成したプログラムの動作検証ができるようになります。

VHDLおすすめ書籍

コメント