FPGAの使い方のお勉強として、今回は『半加算器』をVHDLで作成してみたいと思います。内容としては超簡単なものですが、まずはVHDLの書き方の勉強ということでやってみます。

ちなみに、筆者はFPGA初心者で、備忘録として勉強した内容をブログとして残しているので、多少間違っている点などもあるかもしれませんのでご了承ください。

今回設計するもの

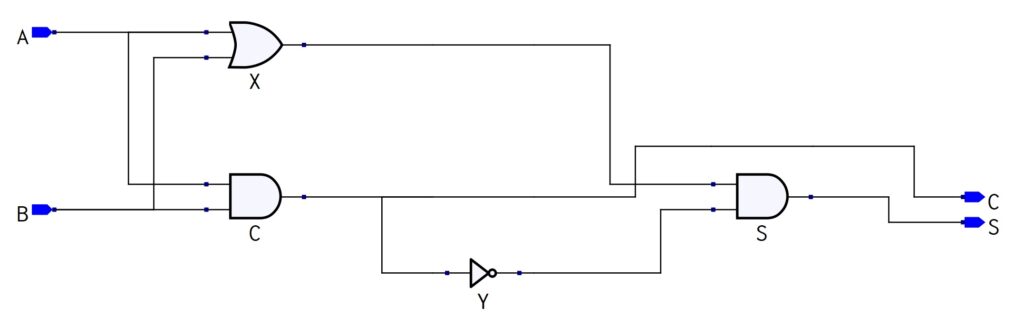

半加算器については、wikipediaなどで調べると詳しく出てくるのでここでは詳しく説明しません。論理回路としては以下のような感じです。

入力A、入力B、出力S(Sum)、桁上げ出力C(carry out)になります。

真理値表としては以下のようになります。

| A | B | C | S |

| 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 0 |

VHDL記述

VHDLで記述するとこんな感じです。

library IEEE; -- ライブラリ宣言。おまじないと思ってとりあえず書く

use IEEE.std_logic_1164.all; -- パッケージ呼び出し。おまじないと思ってとりあえず書く

entity half_adder is -- エンティティ宣言

port( A, B : in std_logic; -- ポート名 : 入力 データタイプ

C, S : out std_logic ); -- ポート名 : 出力 データタイプ

end half_adder;

architecture RTL of half_adder is -- アーキテクチャ宣言

signal X, Y : std_logic; -- 内部信号の定義

begin

X <= A or B;

Y <= A nand B;

C <= not Y;

S <= X and Y;

end RTL;エンティティ宣言

エンティティ宣言はこんな感じのルールで書きます。この部分はこのVHDLファイルの外部からの入力および出力の信号を宣言するイメージです。エンティティ名は任意の文字列で大丈夫ですが、機能などがイメージできる名前にしておくのが良いと思います。

entity 「エンティティ名」 is

「ポート宣言」

end 「エンティティ名」

ポート宣言

エンティティ宣言内のポート宣言は次のように書きます。最後の行だけ「;」は無しで「);」を付けるので注意が必要です。信号名は任意の文字列で大丈夫です。

入出力方向は、in, out, inout, buffer, linkageなどがあるようですが、とりあえずはin, outだけしか使わないと思います。

型は、1データだったらstd_logic、ベクトルデータだったらstd_logic_vectorを使用します。とりあえずは、この2つを覚えておけば良さそうです。

port (

<信号名> : <入出力方向> <型>;

<信号名> : <入出力方向> <型>;

<信号名> : <入出力方向> <型>

);

アーキテクチャ宣言

アーキテクチャ宣言は次のように書きます。アーキテクチャ名は任意の文字列でいいですが、RTLとかbehaviorなどにしておくことが多いようです。

宣言文の部分は、内部で使用する信号、定数、関数などを定義します。

signal:信号

constant:定数

type:型

function:関数

みたいな感じです。他にもあるようですがとりあえずこの辺を抑えておけば良さそうです。

begin の中は同時処理文になります。入力が切り替わったらその瞬間に出力も切り替わるようなイメージです。記述の順番は関係なくなるので注意が必要です。

順番に処理をさせたい場合は、プロセス文というものを使います。別の機会にやりたいと思います。

architecture 「アーキテクチャ名」 of 「エンティティ名」 is

<宣言文>

begin

<同時処理文>

end 「アーキテクチャ名」

コメント