LatticeのFPGA評価ボードの「MachXOブレークアウトボード」を使ってLED点灯をやってみましたので、やり方を解説します。

FPGA初心者の私は、試行錯誤をしてLEDを光らせるまで半日ぐらいかかりましたが、やり方をわかってしまうと10分でできてしまいそうなくらい簡単です。

ちなみに、筆者はFPGA初心者で、備忘録として使い方をブログとして残しているので、多少間違っている点などもあるかもしれませんのでご了承ください。

①プロジェクトファイルを作成する

②Verilogファイルを作成して、コードを書く

③ピン設定をする

④FPGAにプログラムを書き込む

⑤動作確認

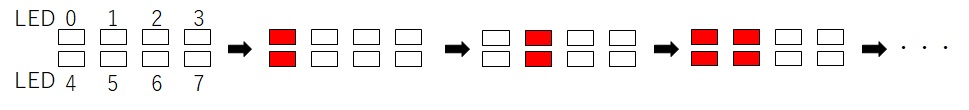

今回実現した動作

今回実現したい動作は、以下になります。

・4個のLED(LED[0]~LED[3])を4桁の2進数に見立て、SWをON(ONエッジ)するたびに、LEDでカウントしていく。

・LED[4]~LED[7]は、LED[0]~LED[3]と連動して同じ動きをする。

プロジェクトファイルの作成

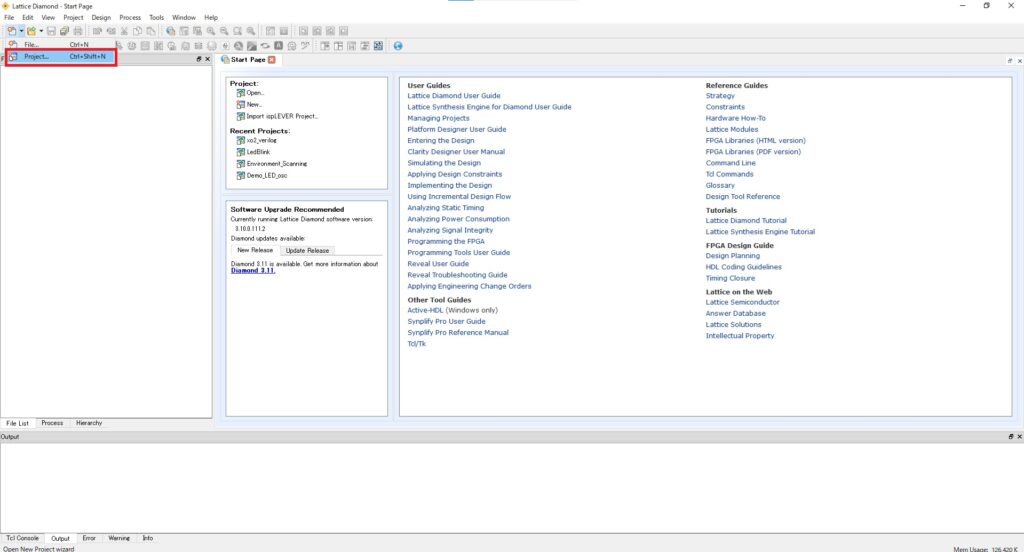

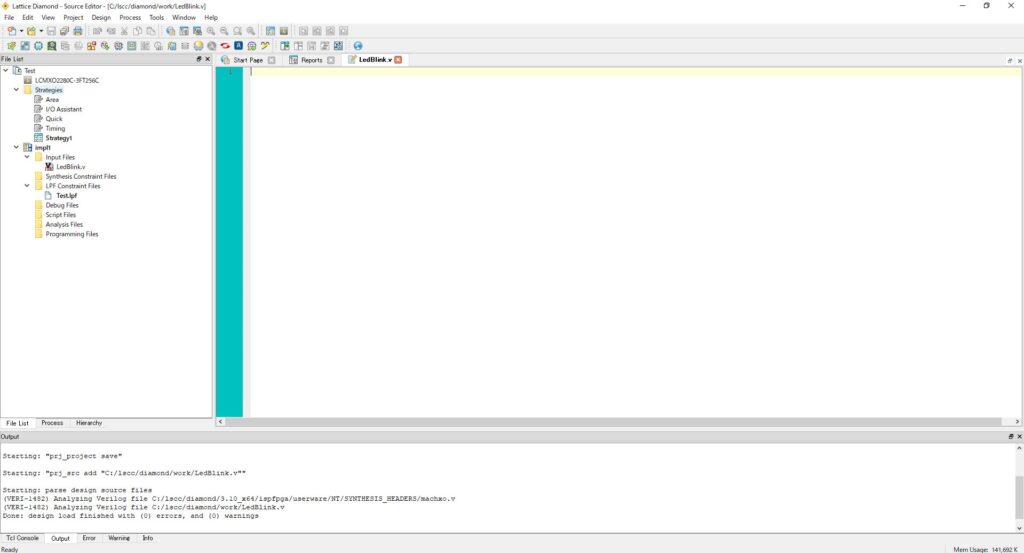

①Lattice Diamondを起動し、新しいプロジェクトを作成

「File」→「New」→「Project」または「Newアイコン」→「Project」

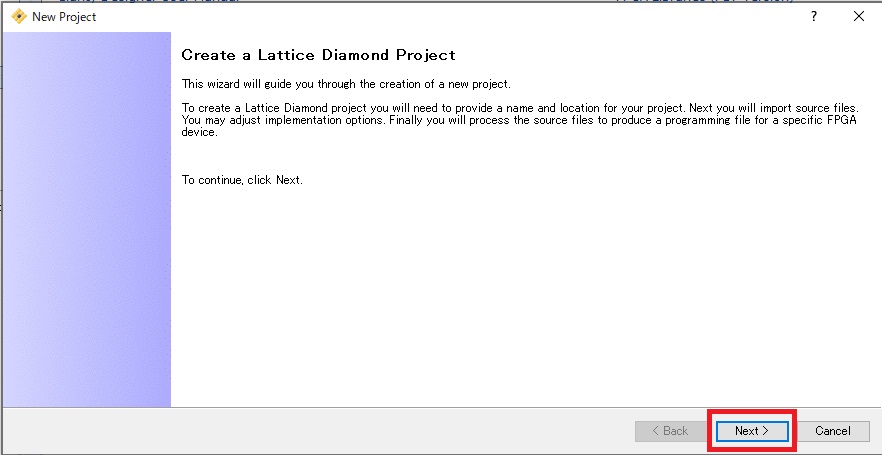

②ガイドが出てくるので「Next」

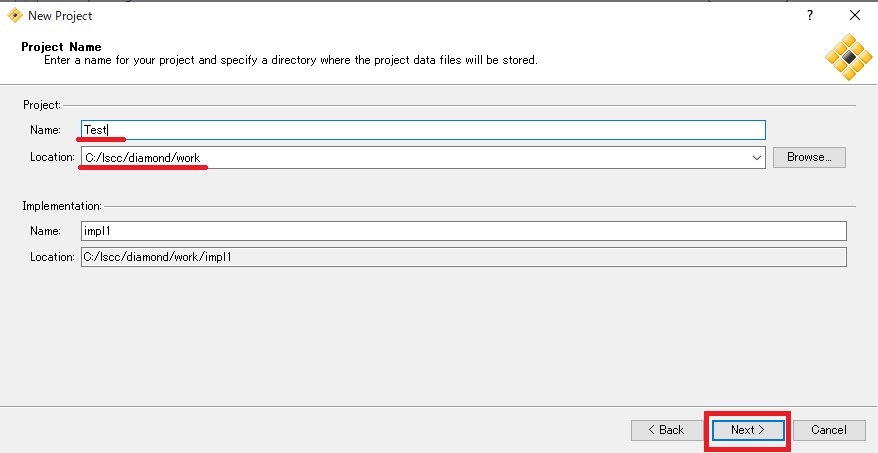

③Project名と保存場所を入力

例ではファイル名は”Test”、保存場所は”C:/lscc/diamond/work”としています。

Project名は英数字だけにしておいた方が良いです。また、保存場所のパスも日本語が入らないように注意した方が良いです。

Implementationはサブproject名みたいな感じですが、今回は特に変えずそのままにしています。

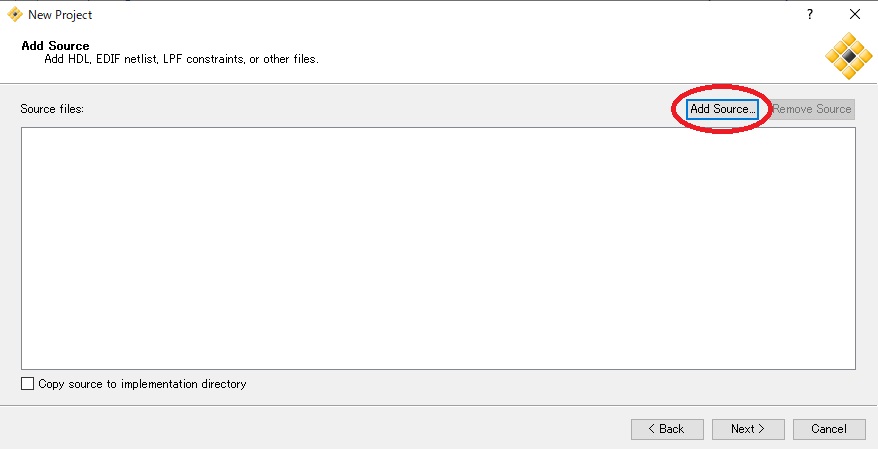

④既存のデザインファイルがあれば読み込みます

既存のデザインファイルがあるようでしたら、「Add Source」から追加することができます。今回は何もないので飛ばしました。

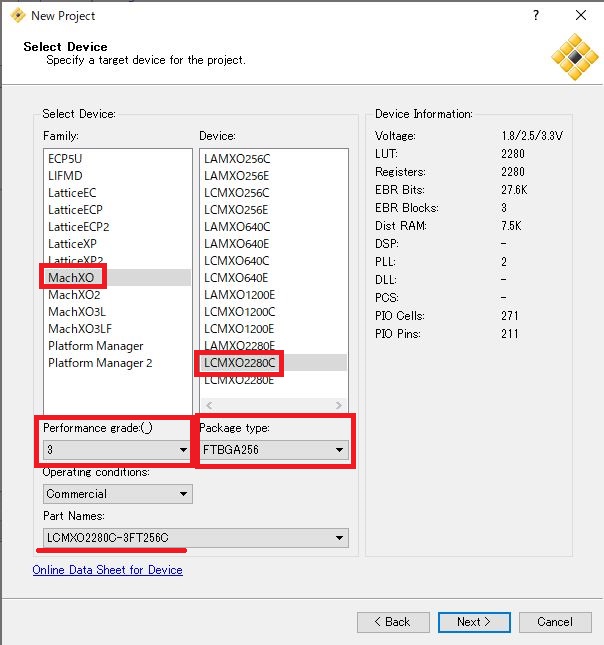

⑤使用するデバイスを選びます

今回のテストボードは、LCMXO2280C-3FTN256Cというデバイスが載っているので、

Family:MachXO

Device:LCMXO2280C

Performance grade:3

Package type:FTBGA256

Operating condition:Commercial

を選びます。一番下の”Part Name”に設定した品番が出てくるのでそちらを確認して、問題なければ「Next」を押します。

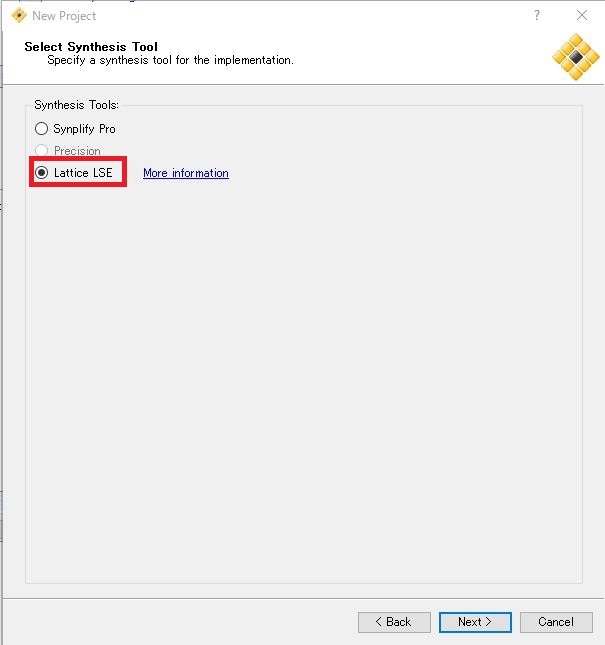

⑥論理合成ツールを選びます

今回は”Lattice LSE”という論理合成ツールを選びました。

ちなみに、”Lattice LSE”はラティスのオリジナル論理合成ツール、”Synplify Pro”はSynopsys社の論理合成ツールです。HPに書いてある感じだと”Synplify Pro”の方がいろいろできそうな感じですが、こちらはおいおい試してみることにします。

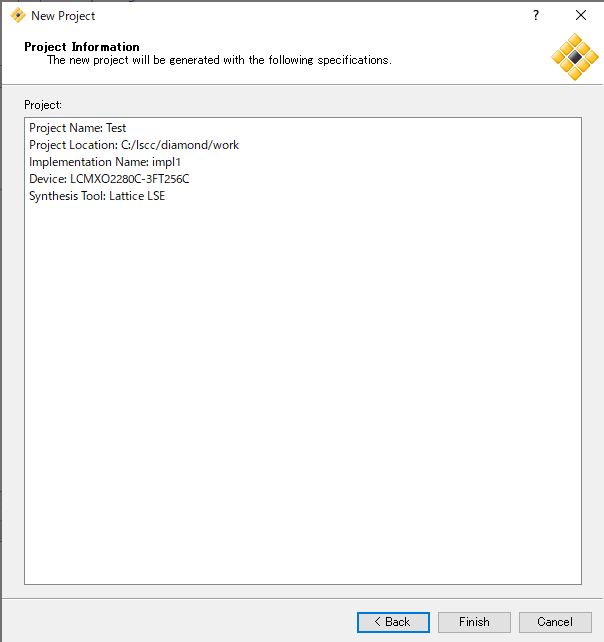

⑦確認し問題なければ「Finish」

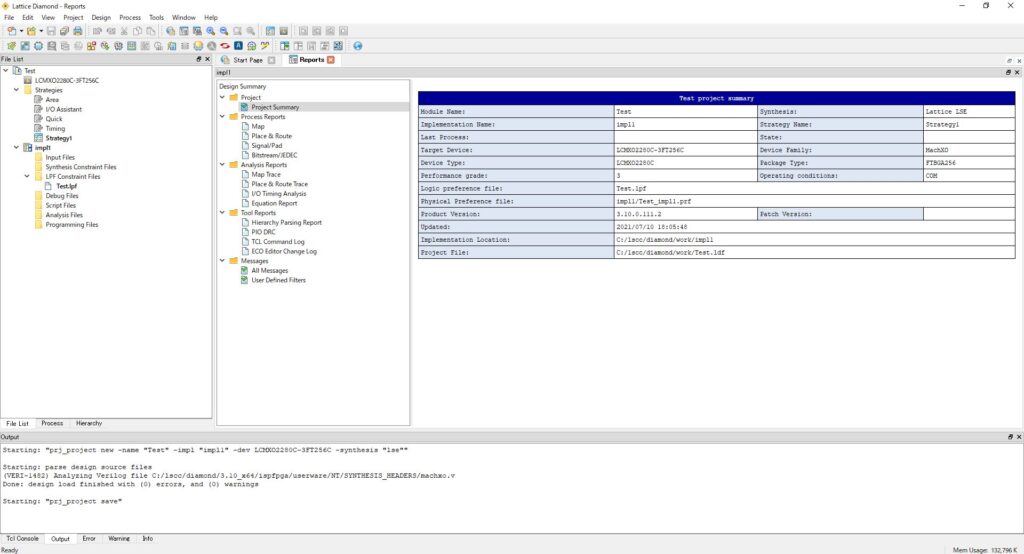

⑧Project作成完了!

こんな感じの画面になります。

Verilogを作成し、コードを書く

実現したい動作をHDLで記述していきます。

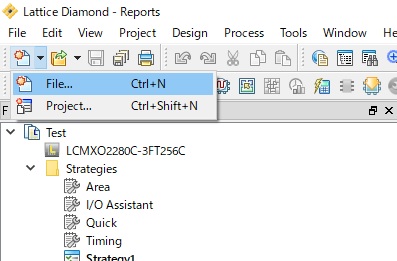

①Verilogファイルを作成

②Verilog Fileを選んでファイル名を入力

今回はVerilogでプログラムを書いていくので”Verilog Fileを選びます。ファイル名は、”LedBlink”としました。

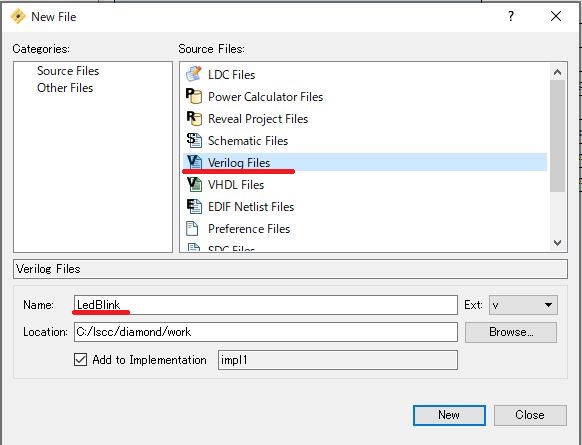

③Verilogのエディタ画面が表示されます

④コードを書いていきます

今回は以下のようなコードとしました。評価ボードの回路は、LEDは出力が”L”の時に光るので、LED[*]は負論理としています。

module LedBlink(SW,LED);

input SW; // 入力

output [7:0]LED; //出力 8bit

reg [3:0]count; // 内部変数 4bit

always @(posedge SW) begin

count <= count + 1; // SWのONエッジ毎にcoutを+1

end

assign LED[0] = ~count[0]; // 1桁目

assign LED[1] = ~count[1]; // 2桁目

assign LED[2] = ~count[2]; // 3桁目

assign LED[3] = ~count[3]; // 4桁目

assign LED[7:4] = LED[3:0]; // 5~8桁目は、1~4桁目と同じ

endmodule⑤コンパイルする

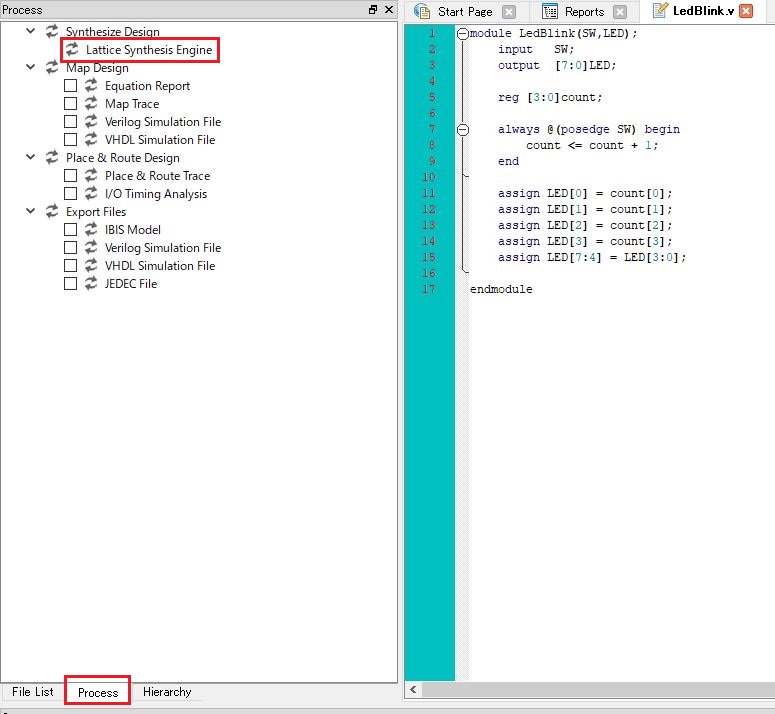

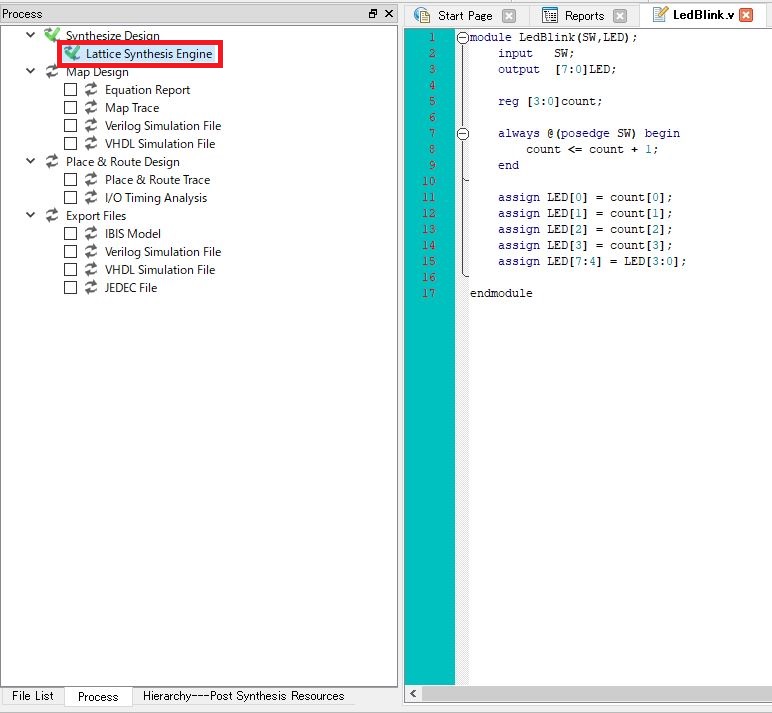

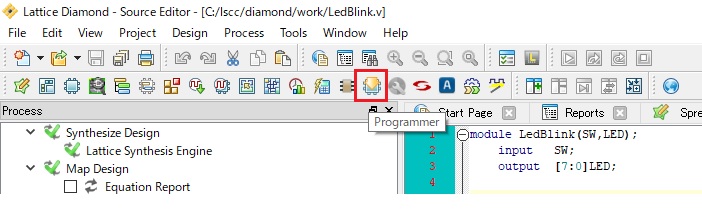

Processウィンドウで、”Process”のタブを選び、一番上の”Lattice Synthesis Engine”をダブルクリックします。コンパイルが始まり、問題なければ、緑のチェックボタンに変わります。

ピン設定をする

入力、出力のピンを設定していきます。

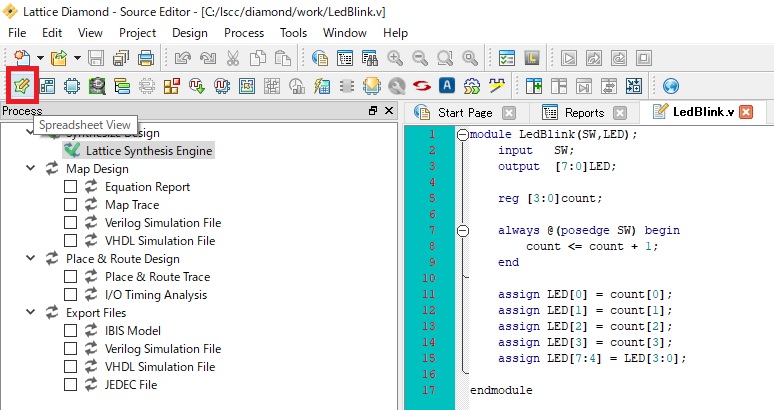

①”Spreadsheet View”を起動します

左上のアイコンをクリックして”Spreadsheet View”を起動します。「Tool」→「Spreadsheet View」からでも起動できます。

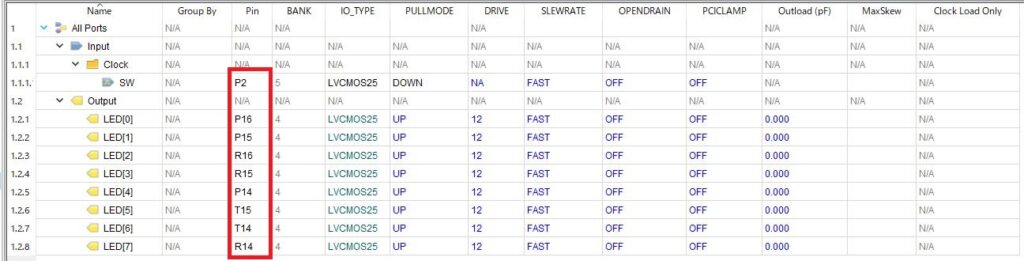

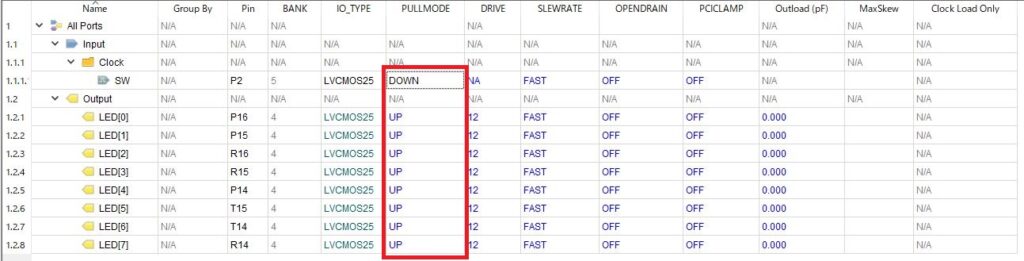

②ピン番号を割り当てる

入力信号(SW)、出力信号(LED[0]~LED[7])にピン番号を割り当てます。今回は「MachXOブレークアウトボード」を使っているので、そちらの回路図から対応するピンを確認します。入力信号については、自分でSWを外付けするので適当なピンを選びました。

③各ピンのPULLMODEを選択する

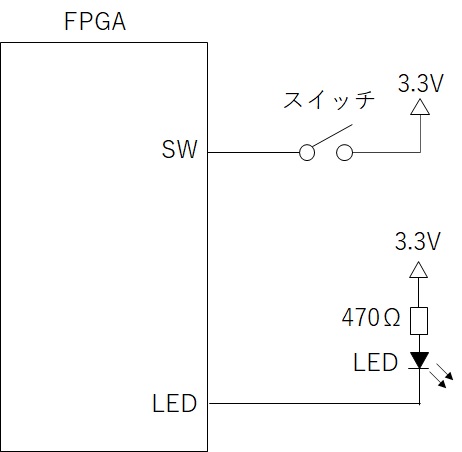

各入出力ピンをプルアップするか、プルダウンするかを選択します。ここについては実際の回路を思い浮かべてやらないとちゃんと動作しないので要注意です。

今回は入力、出力の回路図は以下のようになります。そのため、入力ピンは「プルダウン」、出力ピンは「プルアップ」としています。ちなみに、出力ピンはLow-activeとしています。(Lowの時にLEDが光る)

FPGAにプログラムを書き込む

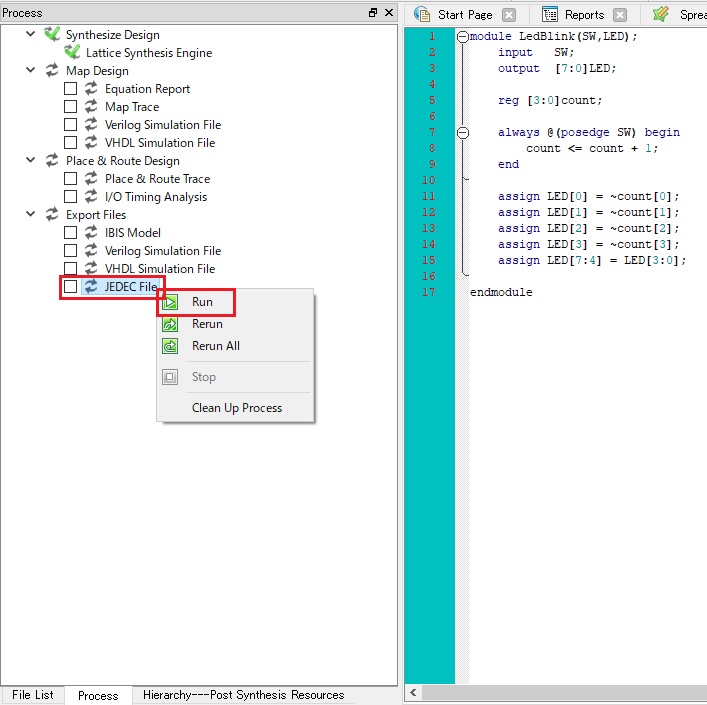

①JEDECファイルを作成する

作成したプログラムを書き込むための”JEDEAC File”を作成します。

Processウィンドウで、「JEDEC File」を右クリックして、「Run」をしてJEDECファイルを作成します。

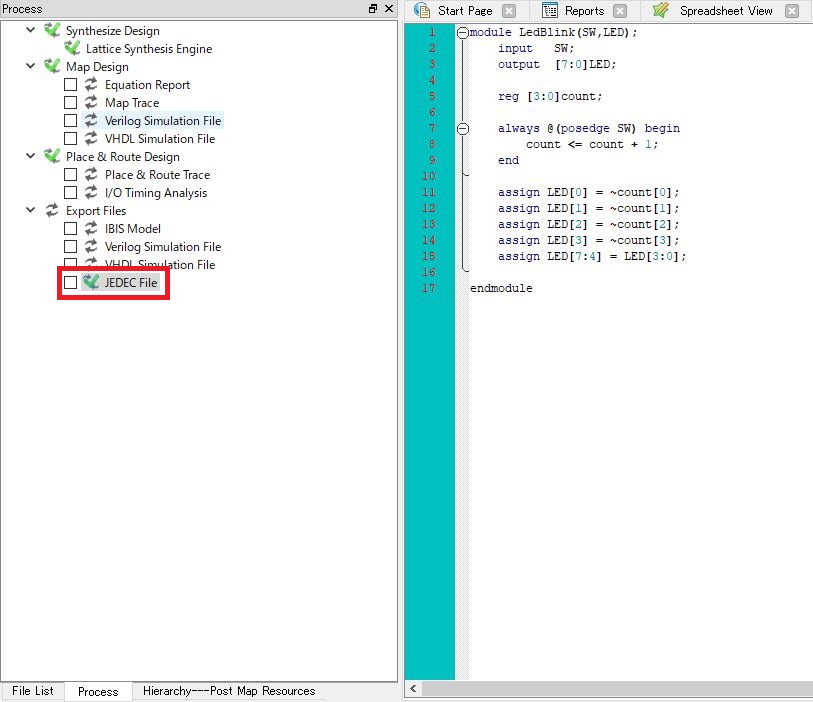

②作成成功したら緑色のチェックに変わる

③”Programmer”を起動します

上のアイコンをクリックして”Programmer”を起動します。「Tool」→「Programmer」からでも起動できます。

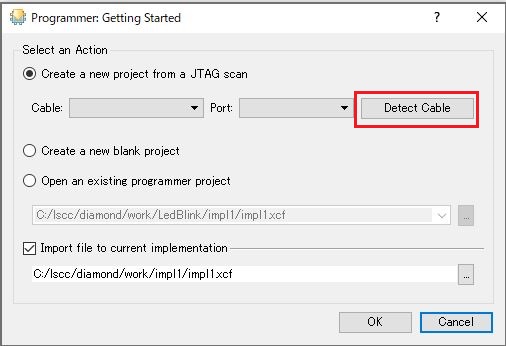

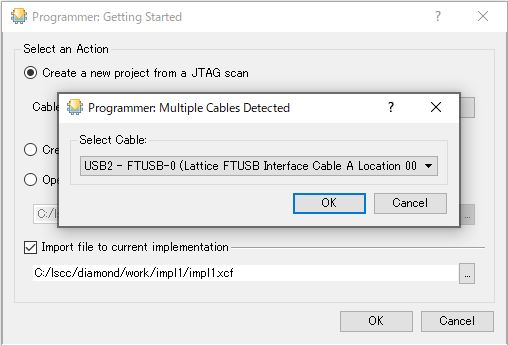

④通信ケーブルを選択します

評価ボードとPCをUSBで接続して、「Detect Cable」を押し、通信ケーブルを選択します。

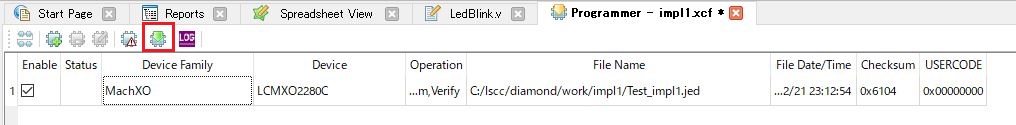

⑤プログラムを書き込む

デバイス名、JEDECファイルのパス等が問題ないか確認し、問題なければプログラムの書き込みを行います。”Program”アイコンをクリックして書き込みを行います。「Design」→「Program」でも書き込みできます。

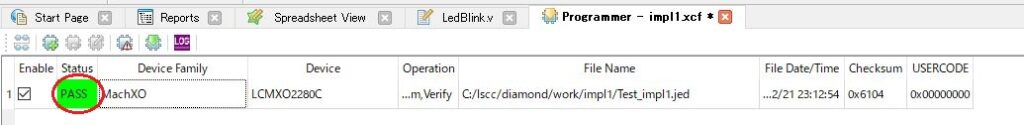

⑥書き込み終了

書き込みに成功すると、Statusの欄が”Pass”と緑色になります。

動作確認

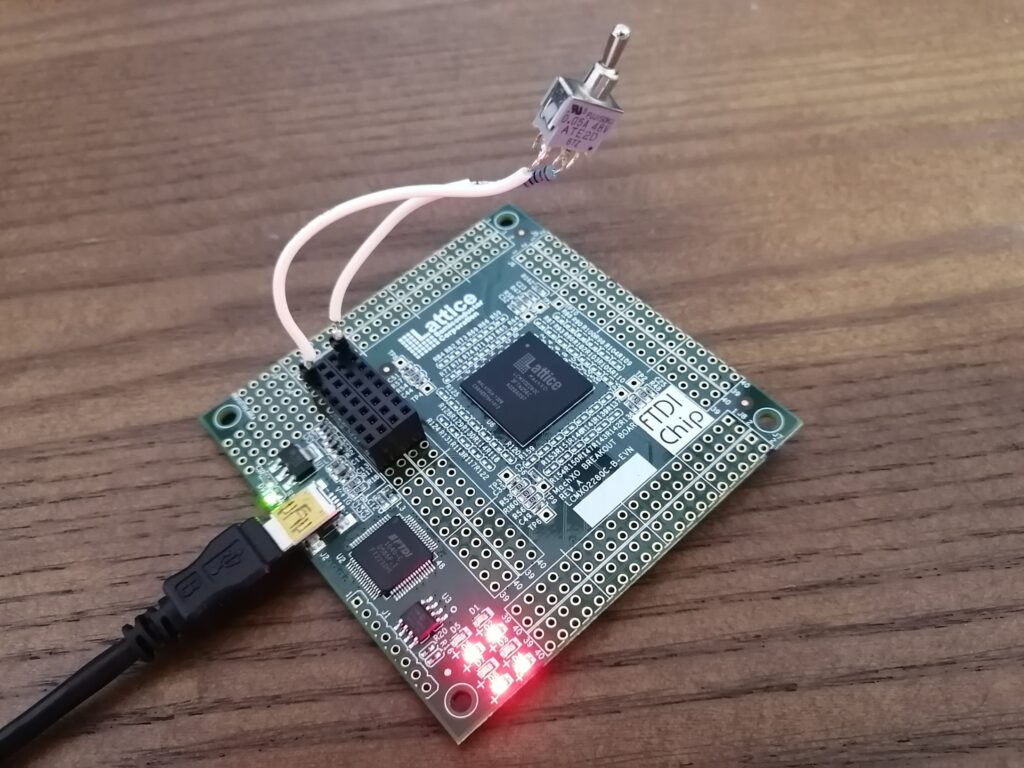

最後にプログラムと動作があっているか、実機で動作確認をします。

こんな感じで簡易的にスイッチを付けて、動作確認を行いました。プログラム自体は問題なさそうですが、スイッチのチャタリングで、たまにカウントが多く進んでしまうことがあります。この辺は今後改善していこうと思います。

Verilog HDLおすすめ書籍

コメント